AMS-VTtm

Analog/Mixed-Signal Virtual Tester

Why Wait for Silicon To Validate Your Test Program?

Use a Virtual ATE in Advance for Faster Delivery,

Easier Debug & Reduced ATE Usage Cost

Your Post-Silicon Test Program & Load Board Validation Is Risky

-

Late delivery

-

Silicon re-spin

-

Customer returns

-

High tester-time cost

-

Limited debug on ATE

When you validate late, you increase the risk.

This is a post-silicon time bomb.

The Analog/Mixed-Signal (AMS) Case Is Even Trickier

Compared to the digital case, validating your AMS test program and load board is more challenging.

• AMS test programs are often manually written → more prone to human error

• Test program code is nonstandard & unstructured → hard to simulate

• Your load board has extra hardware → more complex to debug

• Debug starts only after first-si → risky late validation

These conditions add even more risk to an already complex task.

Expedite Your Debug

for Faster Time to Market

Slash Post-Si Debug Time by up to 90%

Before

After

before

after

AMS Virtual ATE:

-

Emulate the ATE tester

-

Predict post-si test results

-

Debug faster using EDA tools

-

Verify your test program pre-si

-

Validate load board design pre-si

-

Noavoidable re-spins.

-

Noexcessive ATE tester time.

-

Nopreventable customer returns.

-

Nowhopping production test costs.

Just a smooth workflow with predictable test results.

Hello Virtual ATE. Goodbye Risk!

Before

After

Before

After

Before

After

Before

After

Expedite Your Debug

for Faster Time to Market

Slash Post-si Debug Time by up to 90%

“The AMS-VT Virtual ATE has accelerated our time to market by at least a month.”

[Replace with the real testimonial]

John Joe Jones

VP of Engineering

NXP

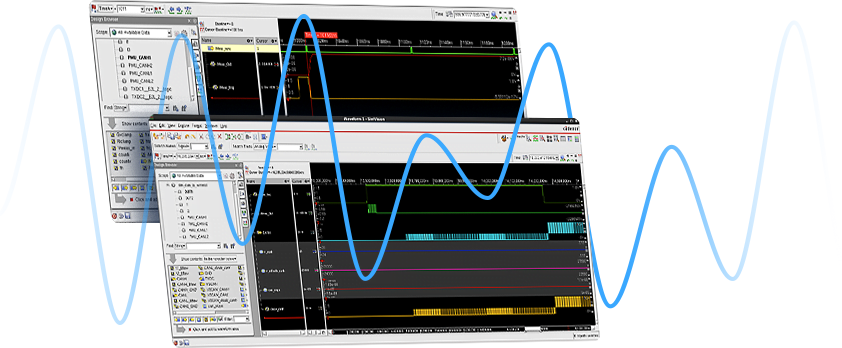

Now You Can Debug in Simulation as if You Were Using the Actual ATE

Get to Market Faster Using Pre-Silicon Test Program & Load Board Validation

AMS-VT™, TestInsight’s AMS Virtual ATE, allows you to debug your test program and load board before silicon arrives. It lets you use the same ATE OS you’re familiar with and seamlessly switch between simulation and the real ATE and DUT. This pre-silicon validation provides the same results as post-silicon ATE, making your production test shorter and more predictable. It improves the chances of tests working the first time, so you can accelerate time to market while saving resources.

Release Your Test Program in Days vs. Weeks/Months

You can also use AMS-VT to accelerate post-silicon test program validation. AMS-VT allows efficient silicon debug supported by simulations, which provide useful internal DUT data that is otherwise inaccessible.

Release Your Test Program in Days vs. Weeks/Months

You can also use AMS-VT to accelerate post-silicon test program validation. AMS-VT allows efficient silicon debug supported by simulations, which provide useful internal DUT data that is otherwise inaccessible.

PLAN FOR

PRODUCTION TEST NOW

PRODUCTION TEST NOW

What You Can Check with AMS-VT

AMS-VT streamlines the flow of your AMS testing project, ensuring that all the different parts are in sync: test program, ATE, DUT and load board. Here is what you can check with AMS-VT long before silicon arrives:

-

1 Validate the test program flow, test result manipulation, and pass/fail states.

-

2 Validate ATE instruments and DUT setup throughout the test execution.

-

3 Confirm ATE-DUT connectivity at every stage of the test program.

-

4 Verify load board programmable elements state such as relays.

-

5 Sync the digital patterns and analog portions of the test.

See How AMS-VT Can Help Your Specific Project

PLAN FOR

PRODUCTION TEST NOW

PRODUCTION TEST NOW

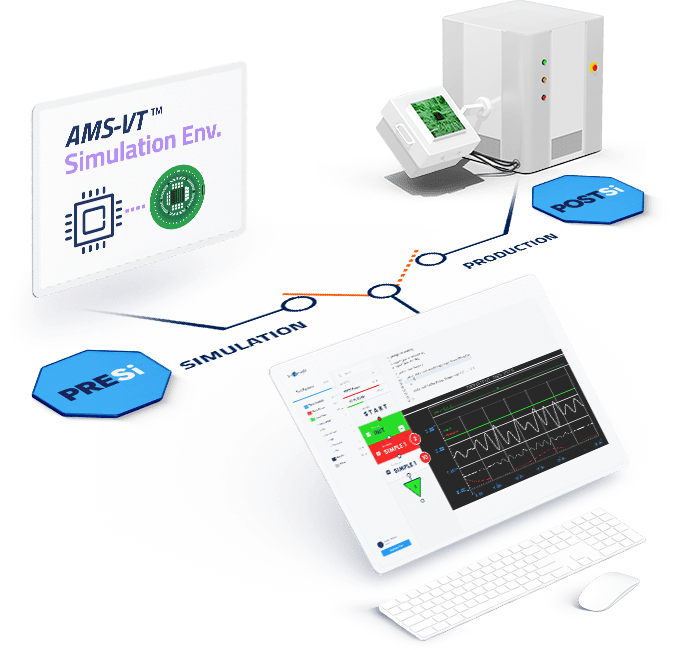

Breakthrough Closed-Loop Technology

Harness the Power of EDA To Deliver a High-quality Test Program Faster

Closed-loop systems are well known for their stability, which is why we applied this concept to test engineering. AMS-VT creates a closed loop between your native ATE operating system and an EDA simulation environment. With this link, you can detect failures much earlier to accelerate test program bring up and debug while improving quality.

How AMS-VT Works

Your ATE OS, such as V93000 SmarTest, connects through AMS-VT to an EDA environment, such as Cadence Spectre AMS simulator. You can set up this closed-loop connection even if you don’t have any knowledge of EDA languages such as Verilog. AMS-VT then works according to this flow, which is also marked in the diagram below:

ATE Operating System

1 Recording all test activity using the ATE activity trace

2 Simulating ATE operations such as:

ATE instrument models driving the DUT signals

ATE instrument models measuring DUT responses

3 Sending the results back to the ATE OS

4 Emulating the test program flow in the offline ATE OS

AMS Simulation Env

1 Recording all test activity using the ATE activity trace

2 Simulating ATE operations such as:

ATE instrument models driving the DUT signals

ATE instrument models measuring DUT responses

3 Sending the results back to the ATE OS

4 Emulating the test program flow in the offline ATE OS

What Is Required To Run AMS-VT?

First and foremost, running AMS-VT requires simulation models of the DUT and load board. Here is the full list of requirements:

-

DUT & load board models

-

Working test program

-

EDA environment

-

ATE OS

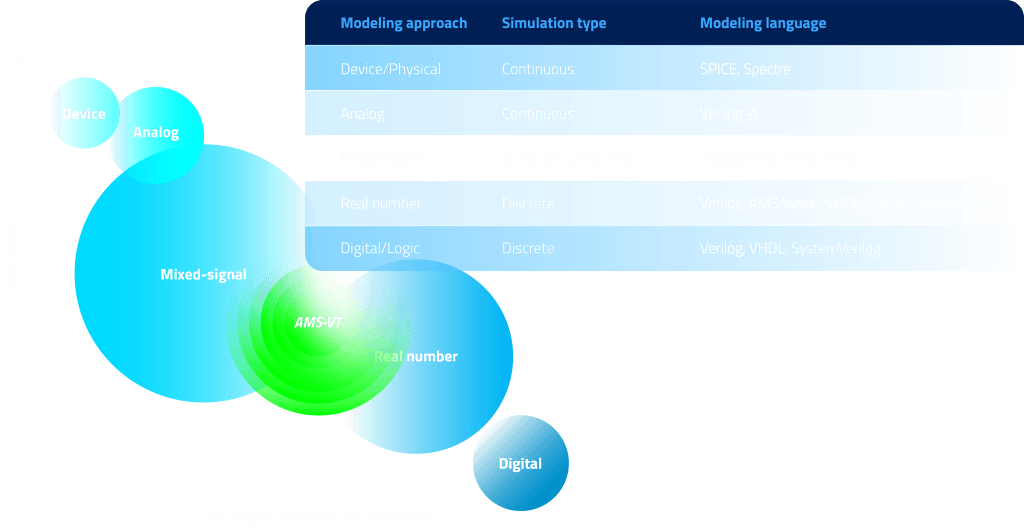

What Is the Effect on Simulation Time When Using AMS-VT?

The overall runtime depends mainly on your DUT simulation time regardless of AMS-VT. On top of that, AMS-VT adds a few percentages of runtime. For example, 25,000 tests of a modern mixed-signal production SoC took AMS-VT about 45 minutes to complete.

AMS-VT performs mixed-signal simulation using behavioral modeling instead of SPICE to achieve accurate test program validation while keeping runtime short. This efficiency is possible because high-level DUT models are sufficient for ATE test program verification. As stated by HDL Design House, “Such a model may be many orders of magnitude faster than the SPICE model, yet sufficiently accurate.”

This graph shows how AMS-VT balances accuracy with simulation performance, hitting the sweet spot between precision and speed.

Have your own

AMS-VT crystal ball

Key Features and Benefits

Faster Delivery, Easier Debug and Reduced ATE Usage Cost

Shorter TTM

Test program & load board are debugged at tapeout

Faster debug

Efficient silicon debug supported by simulations

Reduced Test Cost

ATE readiness enables shorter tester time

Have your own

AMS-VT crystal ball

You May Also Be Interested in...

Gain Confidence in Your

Mixed-Signal Test Program

With a Virtual ATE